u-blox AG Zürcherstrasse 68 8800 Thalwil Switzerland www.u-blox.com

Phone +41 44 722 7444 Fax +41 44 722 7447 info@u-blox.com

# LEA-5 u-blox 5 GPS and GALILEO Modules

Hardware Integration Manual (incl. Reference Design)

#### **Abstract**

This document describes the hardware features and specifications of the u-blox 5 based LEA-5 series of cost effective, high-performance GPS/GALILEO modules.

Features include AssistNow Online and AssistNow Offline A-GPS services, KickStart accelerated acquisition, SuperSense® Indoor GPS providing best-in-class acquisition and tracking sensitivity, precision timing and an innovative jamming-resistant RF architecture. The compact 17.0 x 22.4 mm form factor of the highly successful LEA-4 series is maintained, enabling easy migration. The LEA-5 series supports passive and active antennas.

# Manual

| Title             | LEA-5       | LEA-5                                                             |                                                                               |                          |  |  |  |  |  |  |  |

|-------------------|-------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|--|

| Subtitle          | Hardware Ir | ntegration Manual                                                 |                                                                               | (incl. Reference Design) |  |  |  |  |  |  |  |

| Doc Type          | Manual      | Manual Preliminary                                                |                                                                               |                          |  |  |  |  |  |  |  |

| Doc Id            | GPS.G5-MS   | GPS.G5-MS5-07005 A1                                               |                                                                               |                          |  |  |  |  |  |  |  |

| Revision<br>Index | Date        | Name                                                              | Status / Com                                                                  | ments                    |  |  |  |  |  |  |  |

| Initial Version   | 18/01/2008  | TC                                                                |                                                                               |                          |  |  |  |  |  |  |  |

| Initial Release   | 23/04/2008  | TG                                                                | Addition of Hardware Description, Product Handling, Product Testing, Appendix |                          |  |  |  |  |  |  |  |

| А                 | 19/03/2008  | TG Addition of Reference Design. Update to include Eco Power Mode |                                                                               |                          |  |  |  |  |  |  |  |

| A1                | 23/04/2008  | TG                                                                | USB update                                                                    |                          |  |  |  |  |  |  |  |

This document and the use of any information contained therein, is subject to the acceptance of the u-blox terms and conditions. They can be downloaded from www.u-blox.com. u-blox makes no warranties based on the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice.

u-blox reserves all rights to this document and the information contained herein. Reproduction, use or disclosure to third parties without express permission is strictly prohibited. Copyright © 2008, u-blox AG.

For most recent documents, please visit www.u-blox.com

| Pb | Products marked with this lead-free symbol on the product label comply with the "Directive 2002/95/EC of the European Parliament and the Council on the Restriction of Use of certain Hazardous Substances in Electrical and Electronic Equipment" (RoHS). |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | This is an Electrostatic Sensitive Device (ESD).  Observe precautions for handling.                                                                                                                                                                        |

u-blox proprietary

# **Preface**

# u-blox Technical Documentation

As part of our commitment to customer support, u-blox maintains an extensive volume of technical documentation for our products. In addition to our product-specific technical data sheets, the following manuals are available to assist u-blox customers in product design and development.

- **GPS Compendium:** This document, also known as the GPS book, provides a wealth of information regarding generic GPS questions about system functions and technology.

- **Protocol Specification:** Messages, configuration and functionalities of the u-blox 5 software releases are explained in this document.

- **Hardware Integration Manual:** This Manual provides hardware design instructions and information on how to set up production and final product tests.

# How to use this Manual

The LEA-5 Hardware Integration Manual provides the necessary information to successfully design in and configure these u-blox 5-based GPS/GALILEO receiver modules. For navigating this document please note the following:

This manual has a modular structure. It is not necessary to read it from the beginning to the end. To help in finding needed information, a brief section overview is provided below:

- 1. **Hardware Basics**: This chapter introduces the basics of function and architecture of the LEA 5 modules.

- 2. **Design-In**: This chapter provides the Design-In information necessary for a successful design.

- 3. **Product Handling**: This chapter defines packaging, handling, shipment, storage and soldering.

- 4. **Product Testing**: This chapter provides information about testing of OEM receivers in production.

- 5. **Appendix:** The Appendix includes a Reference Design, guidelines on how to successfully migrate to u-blox 5 designs, and useful information about the different antenna types available on the market and how to reduce interference in your GPS design.

The following symbols are used to highlight important information within the manual:

An index finger points out key information pertaining to module integration and performance.

A warning symbol indicates actions that could negatively impact or damage the module.

# Questions

If you have any questions about u-blox 5 Hardware Integration, please:

- Read this manual carefully.

- Contact our information service on the homepage <a href="http://www.u-blox.com">http://www.u-blox.com</a>

- Read the questions and answers on our FAQ database on the homepage <a href="http://www.u-blox.com">http://www.u-blox.com</a>

# **Technical Support**

# **Worldwide Web**

Our website (www.u-blox.com) is a rich pool of information. Product information, technical documents and helpful FAQ can be accessed 24h a day.

# By E-mail

If you have technical problems or cannot find the required information in the provided documents, contact the nearest of the Technical Support offices by email. Use our service pool email addresses rather than any personal email address of our staff. This makes sure that your request is processed as soon as possible. You will find the contact details at the end of the document.

# **By Phone**

If an email contact is not the right choice to solve your problem or does not clearly answer your questions, call the nearest Technical Support office for assistance. You will find the contact details at the end of the document.

# **Helpful Information when Contacting Technical Support**

When contacting Technical Support please have the following information ready:

- Receiver type (e.g. LEA-5A) and firmware version (e.g. V4.00)

- Receiver configuration

- Clear description of your question or the problem together with a u-center logfile

- A short description of the application

- Your complete contact details

# **Contents**

| Prefa | ce   |                                                                | 3  |

|-------|------|----------------------------------------------------------------|----|

| Conte | ents |                                                                | 5  |

| 1 Ha  | ardv | ware Description                                               | 9  |

| 1.1   |      | nctional Overview                                              |    |

| 1.2   | M    | odule Selector                                                 | 9  |

| 1.3   | Ar   | chitecture                                                     | 10 |

| 2 D   | esig | n-ln                                                           | 11 |

| 2.1   | Ро   | wer Management                                                 | 11 |

| 2.    | 1.1  | Connecting Power                                               | 11 |

| 2.    | 1.2  | Power Modes                                                    | 12 |

| 2.    | 1.3  | V_ANT                                                          | 12 |

| 2.2   | Sy   | stem Functions                                                 | 13 |

| 2.2   | 2.1  | EXTINT - External Interrupt Pin                                | 13 |

| 2.2   | 2.2  | System Monitoring                                              | 13 |

| 2.3   | Int  | erfaces                                                        | 13 |

| 2.3   | 3.1  | Serial                                                         | 13 |

| 2.3   | 3.2  | USB                                                            | 13 |

| 2.3   | 3.3  | Display Data Channel (DDC)                                     | 14 |

| 2.3   | 3.4  | Synchronous Peripheral Interface (SPI)                         | 15 |

| 2.4   | I/C  | Pins                                                           | 15 |

| 2.4   | 4.1  | RESET_N                                                        | 15 |

| 2.4   | 4.2  | EXTINTO                                                        | 15 |

| 2.4   | 4.3  | AADET0_N                                                       | 15 |

| 2.4   | 4.4  | Configuration Pins (CFG_COM0, CFG_COM1, CFG_GPS0)              | 16 |

| 2.5   | De   | sign-In                                                        | 17 |

| 2.5   | 5.1  | Schematic Design-In Checklist for LEA-5                        | 17 |

| 2.6   | LE.  | 4-5 Design                                                     | 18 |

| 2.6   | 5.1  | LEA-5 Passive Antenna Design (LEA-5-H, LEA-5S, LEA-5A, LEA-5T) | 18 |

| 2.6   | 5.2  | Passive Antenna Design (LEA-5-Q, LEA-5M)                       | 21 |

| 2.7   | La   | yout Design-In Checklist                                       | 23 |

| 2.8   | La   | yout                                                           | 23 |

| 2.8   | 3.1  | Footprint                                                      | 23 |

| 2.8   | 3.2  | Paste Mask                                                     | 24 |

| 2.8.3   | Placement                                                   | 25 |

|---------|-------------------------------------------------------------|----|

| 2.8.4   | Antenna Connection and Grounding Plane Design               | 26 |

| 2.8.5   | Antenna Micro Strip                                         | 27 |

| 2.9 Ar  | ntenna and Antenna Supervisor                               | 28 |

| 2.9.1   | Passive Antenna                                             | 29 |

| 2.9.2   | Active Antenna (LEA-5-H, LEA-5S, LEA-5A, LEA-5T)            | 29 |

| 2.9.3   | Active Antenna (LEA-5-Q, LEA-5M)                            | 30 |

| 2.9.4   | Active Antenna Bias Power (LEA-5-H, LEA-5S, LEA-5A, LEA-5T) | 31 |

| 2.9.5   | Active Antenna Supervisor (LEA-5-H, LEA-5S, LEA-5A, LEA-5T) | 31 |

| 3 Produ | uct Handling                                                | 35 |

|         | ackaging                                                    |    |

| 3.1.1   | Reels                                                       | 35 |

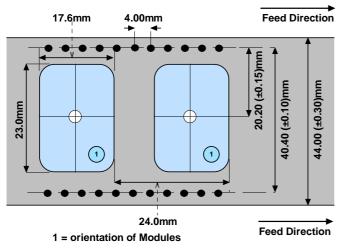

| 3.1.2   | Tapes                                                       | 36 |

| 3.2 Sh  | nipment, Storage and Handling                               | 36 |

| 3.2.1   | Handling                                                    | 36 |

| 3.2.2   | Shipment                                                    | 36 |

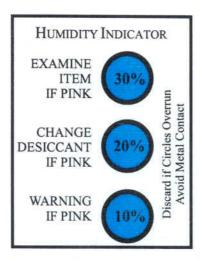

| 3.2.3   | Storage                                                     | 37 |

| 3.2.4   | Handling                                                    | 37 |

| 3.2.5   | Floor Life                                                  | 38 |

| 3.3 Pr  | ocessing                                                    | 39 |

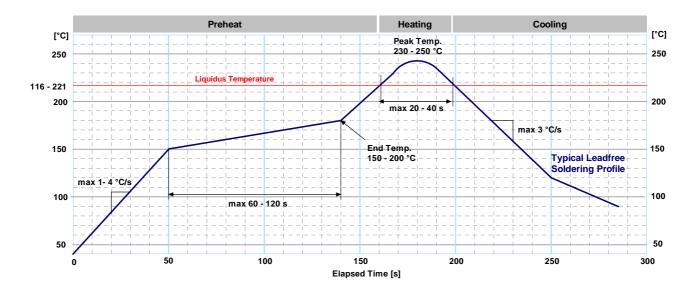

| 3.3.1   | Moisture Preconditioning                                    | 39 |

| 3.3.2   | Soldering Paste                                             | 39 |

| 3.3.3   | Reflow Soldering                                            | 40 |

| 3.3.4   | Optical Inspection                                          | 41 |

| 3.3.5   | Cleaning                                                    | 42 |

| 3.3.6   | Repeated Reflow Soldering                                   | 42 |

| 3.3.7   | Wave Soldering                                              | 42 |

| 3.3.8   | Hand Soldering                                              | 42 |

| 3.3.9   | Rework                                                      | 42 |

| 3.3.10  | Conformal Coating                                           | 43 |

| 3.3.11  | Casting                                                     | 43 |

| 3.3.12  | Grounding Metal Covers                                      | 43 |

| 3.3.13  | Use of Ultrasonic Processes                                 | 43 |

| 4 Produ | uct Testing                                                 | 44 |

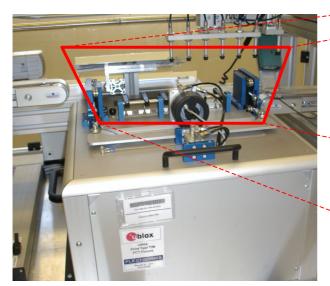

| 4.1 u-  | blox In-Series Production Test                              | 44 |

| 4.2 Te  | est Parameters for OFM Manufacturer                         | 44 |

| 4.3   | System Sensitivity Test                     | 45 |

|-------|---------------------------------------------|----|

| 4.3   | 3.1 Guidelines for Sensitivity Tests        | 45 |

| 4.3   | 3.2 'Go/No go' tests for integrated devices | 45 |

| Appei | ndix                                        | 46 |

| A M   | igration to u-blox-5 Receivers              | 46 |

| A.1   | Migration from LEA-4H / LEA-4P to LEA-5H    | 47 |

| B Re  | eference Design                             | 49 |

| B.1   | LEA-5 Smart Antenna                         | 49 |

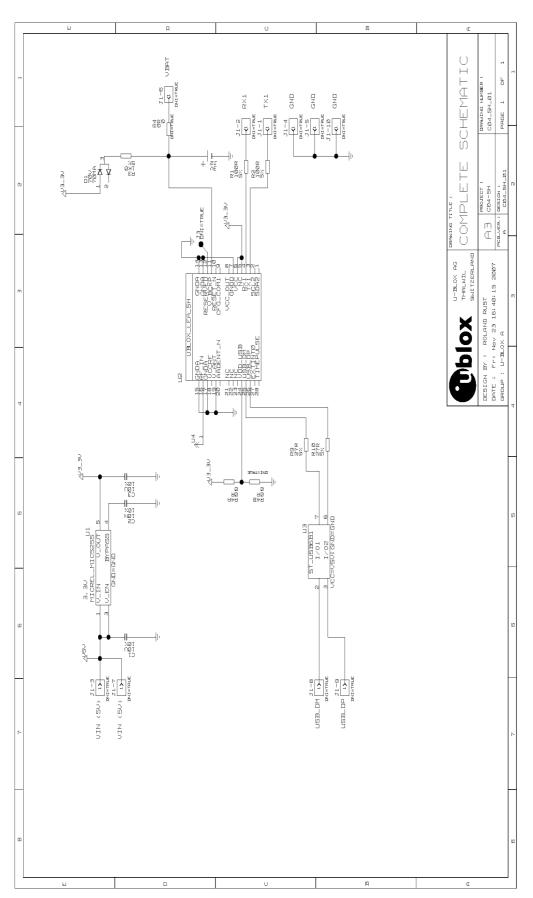

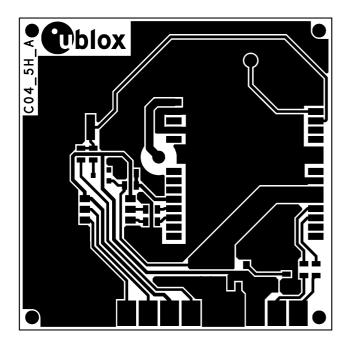

| B.1   | 1.1 Schematic                               | 5C |

| B.1   | 1.2 Bill of Material                        | 51 |

| B.1   | 1.3 Layout                                  | 52 |

| C Ar  | ntennas                                     | 53 |

| C.1   | Selecting the right Antenna                 | 53 |

| C.2   | Active and Passive Antennas                 | 54 |

| C.3   | Patch Antennas                              | 54 |

| C.4   | Helix Antennas                              | 56 |

| C.5   | Helix or Patch, which selection is best?    | 56 |

| C.6   | Antenna Matching                            | 57 |

| C.7   | Antenna Placement                           | 58 |

| D In  | terference Issues                           | 59 |

| D.1   | Sources of Noise                            | 59 |

| D.2   | Eliminating Digital Noise Sources           | 60 |

| D.2   | 2.1 Power and Ground Planes                 | 60 |

| D.2   | 2.2 High Speed Signal Lines                 | 61 |

| D.2   | 2.3 Decoupling Capacitors                   | 61 |

| D.3   | Shielding                                   | 63 |

| D.3   | 3.1 Feed through Capacitors                 | 63 |

| D.3   | 3.2 Shielding Sets of Sub-System Assembly   | 65 |

| E Lis | sts                                         | 66 |

| E.1   | List of Figures                             | 66 |

| E.2   | List of Tables                              | 67 |

| F GI  | lossary                                     | 68 |

| Related Documents | 68 |

|-------------------|----|

|                   |    |

| Contact           | 69 |

# 1 Hardware Description

# 1.1 Functional Overview

The LEA-5 module series is a family of self-contained GPS and GALILEO receivers featuring the powerful 50-channel u-blox 5 positioning engine. These modules provide exceptional GPS performance in a compact form factor and at an economical price. u-blox 5 sets a new standard in GPS receiver technology. A 32-channel acquisition engine with over 1 million effective correlators is capable of massive parallel searches across the time/frequency space. This enables a Time To First Fix (TTFF) of less than 1 second, while long correlation/dwell times make possible the best-in-class acquisition and tracking sensitivity. Once acquired, satellites are passed on to a dedicated tracking engine. This arrangement allows the GPS engine to simultaneously track up to 16 satellites while searching for new ones. u-blox 5's advanced jamming suppression mechanism and innovative RF architecture provide a high level of immunity to jamming, ensuring maximum GPS performance. u-blox 5 has been designed to be able to support the GALILEO system currently being developed by European authorities. The capability of receiving GALILEO L1 signals will provide increased coverage and even better positioning accuracy when this system comes into operation.

With the LEA-5 series the complete signal processing chain from antenna input to serial output is contained within a single component. LEA-5 modules maintain the compact 17.0 x 22.4 mm form factor of their highly successful LEA-4 predecessors. The LEA-5 modules have been designed with backwards compatibility in mind, enabling ease of upgrade and reducing engineering and design costs.

Their small size makes LEA-5 modules the ideal GPS solution for applications with stringent space requirements. The packaging makes expensive RF cabling obsolete, with the RF input being available directly on a pin. The LEA-5 series are SMT solderable and can be handled by standard pick and place equipment.

LEA-5 modules come equipped with a serial port, which can handle NMEA and UBX proprietary data formats, as well as a high speed USB port. The optional FLASH EPROM provides the capacity to store user-specific configuration settings as well as future software updates.

All LEA-5 modules are RoHS compliant (lead-free).

The LEA-5 series of GPS/GALILEO receiver modules are not designed for life saving or supporting devices or for aviation and should not be used in products that could in any way negatively impact the security or health of the user or third parties or that could cause damage to goods.

# 1.2 Module Selector

u-blox provides several modules using the popular and industry standard LEA Form factor. To select the right product for your design consider Table 1:

|        | Voltage Range (V) | Thickness (mm) | 50-channel<br>engine | KickStart | SuperSense | FW Update<br>/ FLASH | Low Power<br>Modes | UART | USB | SPI | DDC | AssistNow<br>Online | AssistNow<br>Offline | Dead Reckoning | Raw Data | Precision Timing | 1PPS | CFG Pins | Reset Input | Antenna<br>Supply | Antenna<br>Supervisor |

|--------|-------------------|----------------|----------------------|-----------|------------|----------------------|--------------------|------|-----|-----|-----|---------------------|----------------------|----------------|----------|------------------|------|----------|-------------|-------------------|-----------------------|

| LEA-5H | 2.7-3.6           | 3.0            | ✓                    | ✓         | ✓          | ✓                    | Р                  | 1    | 1   |     | 1   | ✓                   | ✓                    |                |          |                  | ✓    |          | ✓           | ✓                 | <b>✓</b>              |

| LEA-5S | 2.7-3.6           | 3.0            | ✓                    | ✓         | ✓          |                      | Р                  | 1    | Р   |     | 1   | ✓                   | ✓                    |                |          |                  | ✓    | 1        | ✓           | ✓                 | ✓                     |

| LEA-5A | 2.7-3.6           | 3.0            | ✓                    |           | ✓          |                      | Р                  | 1    | Р   |     | 1   | ✓                   | ✓                    |                |          |                  | ✓    | 1        | ✓           | ✓                 | ✓                     |

| LEA-5Q | 2.7-3.6           | 2.4            | ✓                    | ✓         | ✓          |                      | Р                  | 1    | 1   | 1   | 1   | ✓                   | ✓                    |                |          |                  | ✓    | 3        | ✓           |                   |                       |

| LEA-5M | 2.7-3.6           | 2.4            | ✓                    |           | ✓          |                      | Р                  | 1    | 1   |     | 1   | ✓                   | ✓                    |                |          |                  | ✓    | 2        | ✓           |                   |                       |

| LEA-5T | 2.7-3.6           |                | ✓                    | ✓         | ✓          | ✓                    |                    | 1    | 1   |     | 1   | ✓                   | ✓                    |                |          | ✓                | ✓    |          | ✓           | ✓                 | ✓                     |

P= Planned availability Q1/09

Table 1: Features of the LEA-5 Series

# 1.3 Architecture

LEA-5 modules are divided into two distinct, separately shielded sections. The smaller section is the RF- Section, the larger section contains the Baseband. See Figure 1 for a block diagram of the LEA-5 series.

The RF Front-End contains the integrated Low Noise Amplifier (LNA), the SAW bandpass filter, the u-blox 5 RF-IC and the TCXO or XTO crystal.

The Baseband section contains the digital circuitry comprised of the u-blox 5 Baseband processor, the RTC crystal and additional elements such as the optional FLASH EPROM for enhanced programmability and flexibility.

Figure 1: LEA-5 Block Diagram

# 2 Design-In

For migrating existing ANTARIS®4 product designs to u-blox 5 please refer to Appendix A.

In order to obtain good performance with a GPS receiver module, there are a number of points that require careful attention during the design-in. These include:

- Power Supply

Good performance requires a clean and stable power supply.

- Interfaces

Ensure correct wiring, rate and message setup on the module and your host system.

- Antenna interface

For optimal performance seek short routing, matched impedance and no stubs.

# 2.1 Power Management

# 2.1.1 Connecting Power

u-blox 5 receivers have three power supply pins: VCC, V\_BCKP and VDDUSB.

#### 2.1.1.1 VCC - Main Power

The main power supply is fed through the **VCC** pin. During operation, the current drawn by the u-blox 5 GPS module can vary by some orders of magnitude, especially, if low-power operation modes are enabled. It is important that the system power supply circuitry is able to support the peak power (see datasheet for specification) for a short time. In order to define a battery capacity for specific applications the sustained power figure shall be used.

#### 2.1.1.2 V BCKP - Backup Battery

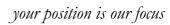

In case of a power failure on pin **VCC**, the real-time clock and backup RAM are supplied through pin **V\_BCKP**. This enables the u-blox 5 receiver to recover from a power failure with either a Hotstart or a Warmstart (depending on the duration of **VCC** outage) and to maintain the configuration settings. If no backup battery is connected, the receiver performs a Coldstart at power up.

If no backup battery available connect the **V BCKP** pin to **GND** (or **VCC**).

As long as **VCC** is supplied to the u-blox 5 receiver, the backup battery is disconnected from the RTC and the backup RAM in order to avoid unnecessary battery drain (see Figure 2). Power to RTC and BBR is supplied from **VCC** in this case.

Figure 2: Backup Battery and Voltage

# 2.1.1.3 VDD\_USB - USB Interface Power Supply

**VDD\_USB** supplies the I/Os of the USB interface. If the USB interface is not used, the **VDD\_USB** pin must be connected to GND. For more information regarding the correct handling of **VDD\_USB** see section 2.3.2.1

#### 2.1.2 Power Modes

u-blox 5 technology offers power optimized architecture with built-in autonomous power saving functions. The receiver uses Autonomous Power Management to minimize the power consumption at any given time. Furthermore, the software shuts down the clock supply to unused peripheral on-chip blocks.

# 2.1.3 **V\_ANT**

LEA-5 modules supporting active antenna supply and supervision use the pin  $\mathbf{V}_{-}\mathbf{ANT}$  to supply the active antenna. Use a 10R resistor in front of  $\mathbf{V}_{-}\mathbf{ANT}^{1}$ . See chapter 2.9.

\_

<sup>&</sup>lt;sup>1</sup> Only applies to LEA-5 modules supporting active antenna supply and supervision.

# 2.2 System Functions

# 2.2.1 EXTINT - External Interrupt Pin

**EXTINTO** is an external interrupt pin. It is used for the time mark function on LEA-5T and will be used in future LEA-5 releases for wake-up functions in low-power modes.

# 2.2.2 System Monitoring

The u-blox 5 GPS and GALILEO Receiver provides System Monitoring functions that allow the operation of the embedded processor and associated peripherals to be supervised. These System Monitoring functions are being output as part of the UBX protocol, class 'MON'.

Please refer to the *u-blox 5 Protocol Specification* [1]. For more information on UBX messages, serial interfaces for design analysis and individual system monitoring functions.

# 2.3 Interfaces

# **2.3.1 Serial**

UART 1 (**RxD1/TxD1**) is the default serial interface. It supports data rates from 4.8 to 230.4 kBit/s. The signal output levels are 0 V to VCC (or VDDIO where available). An interface based on RS232 standard levels (+/- 12 V) can be realized using level shifters such as Maxim MAX3232.

The **RxD1** has fixed input voltage thresholds, which do not depend on **VCC** (see *LEA-5 Data Sheet* [3]). Leave open if unused.

Hardware handshake signals and synchronous operation are not supported.

For the default settings see the LEA-5 Data Sheet [3].

#### 2.3.2 USB

The u-blox 5 USB interface supports the full-speed data rate of 12 Mbit/s.

#### 2.3.2.1 USB external components

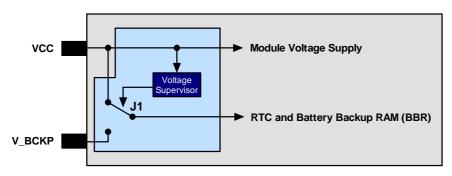

The USB interface requires some external components in order to implement the physical characteristics required by the USB 2.0 specification. These external components are shown in Figure 3 and listed in Table 3.

In order to comply with USB specifications, VBUS must be connected through a LDO (U1) to pin **VDD\_USB** of the module.

If the USB device is **self-powered** it is possible that the power supply (VCC) is shut down and the Baseband-IC core is not powered. Since VBUS is still available, it still would be signaled to the USB host that the device is present and ready to communicate. This is not desired and thus the LDO (U1) should be disabled using the enable signal (EN) of the VCC-LDO or the output of a voltage supervisor. Depending on the characteristics of the LDO (U1) it is recommended to add a pull-down resistor (R11) at its output to ensure **VDD\_USB** is not floating if LDO (U1) is disabled or the USB cable is not connected i.e. VBUS is not supplied.

If the device is **bus-powered**, LDO (U1) does not need an enable control.

Table 2 lists the present availability of USB on LEA-5 modules. Check the **CFG\_COM0** configuration pin (available with LEA-5Q and LEA-5M) to select between Self and Bus Powered modes. For more information on configuration see the *LEA-5 Data Sheet* [3].

|        | Bus Powered | Self Powered |

|--------|-------------|--------------|

| LEA-5H | •2          | •            |

| LEA-5S | Р           | ×            |

| LEA-5A | Р           | ×            |

| LEA-5Q | Р           | •            |

| LEA-5M | Р           | •            |

| LEA-5T | •           | •            |

<sup>•=</sup> Supported

Table 2: USB availability on LEA-5 modules

Figure 3: USB Interface

| Name        | Component                          | Function                                                | Comments                                                                                                                                                                                                                                                                                 |

|-------------|------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U1          | LDO                                | Regulates VBUS (4.45.25 V) down to a voltage of 3.3 V). | Almost no current requirement (~1 mA) if the GPS receiver is operated as a USB self-powered device, but if bus-powered LDO (U1) must be able to deliver the maximum current of ~150 mA. A low-cost DC/DC converter such as LTC3410 from Linear Technology may be used as an alternative. |

| C23,<br>C24 | Capacitors                         |                                                         | Required according to the specification of LDO U1                                                                                                                                                                                                                                        |

| D2          | Protection<br>diodes               | Protect circuit from overvoltage / ESD when connecting. |                                                                                                                                                                                                                                                                                          |

| R4, R5      | Serial<br>termination<br>resistors | Establish a full-speed driver impedance of 2844 Ohms    | A value of 27 Ohms is recommended.                                                                                                                                                                                                                                                       |

| R11         | Resistor                           | Ensures stable signal at VDD_USB.                       |                                                                                                                                                                                                                                                                                          |

**Table 3: Summary of USB external components**

# 2.3.3 Display Data Channel (DDC)

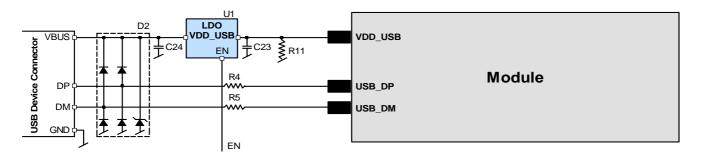

A DDC interface (**SDA2 / SCL2**) is available for communication with the host. Pins **SDA2** and **SCL2** have internal pull-ups.

**x**= Not supported

P= Planned availability Q1/09

<sup>&</sup>lt;sup>2</sup> Supported with Firmware V 4.01 and above.

No pull-up resistors are required if the module is used as a DDC/l<sup>2</sup>C slave (see Figure 4).

Figure 4: Connecting Module as DDC Slave

No Master Mode: External memory is not supported at this time.

# 2.3.4 Synchronous Peripheral Interface (SPI)

The SPI interface allows to interface to a host CPU. In slave mode a single chip select signal enables communication with the host.

No Master Mode: External memory is not supported at this time.

# 2.4 I/O Pins

# 2.4.1 **RESET\_N**

As with ANTARIS 4 versions, LEA-5 modules come equipped with a **RESET\_N** pin. Driving the signal low at **RESET\_N** activates a hardware reset of the system. Unlike LEA-4x modules, **RESET\_N** is not an I/O with LEA-5. It is only an input and will not reset external circuitry.

Use components with open drain output (i.e. with buffer or voltage supervisor).

There is an internal pull up resistor of 3k3 to VCC inside the module that requires that the reset circuitry can deliver enough current (e.g. 1mA).

**RESET\_N** is provided with LEA-5 modules to provide Reset compatibility with ANTARIS 4 versions. Future LEA models may not include this pin and it is therefore not recommended to use it. The preferred option for executing a hardware reset is to send software commands (CFG-RST).

Do not drive **RESET\_N** high.

#### 2.4.2 **EXTINTO**

**EXTINTO** is an external interrupt pin with fixed input voltage thresholds independent of VCC (see the *LEA-5 Data Sheet* [3]). Leave open if unused.

# 2.4.3 AADETO N

**AADETO\_N** is an input pin and is used to report whether an external circuit has detected a external antenna or not. Low means antenna has been detected. High means no external antenna has been detected.

See chapter 2.9.5 for an implementation example.

# 2.4.4 Configuration Pins (CFG\_COM0, CFG\_COM1, CFG\_GPS0)

ROM-based modules provide up to 3 pins (**CFG\_COM0, CFG\_COM1, CFG\_GPS0**) for boot-time configuration. These become effective immediately after start-up. Once the module has started, the configuration settings can be modified with UBX configuration messages. The modified settings remain effective until power-down or reset. If these settings have been stored in battery-backup RAM, then the modified configuration will be retained, as long as the backup battery supply is not interrupted.

Some configuration pins are shared with other functions, e.g. SPI. During start-up, the module reads the state of the configuration pins. Afterwards the other functions can be used.

For more information about settings and messages see the LEA-5 Data Sheet [3].

# 2.5 Design-In

This section provides a Design-In Checklist as well as Reference Schematics for new designs with u-blox 5. For migration of existing ANTARIS<sup>®</sup>4 product designs to u-blox 5 please refer to Appendix A.

# 2.5.1 Schematic Design-In Checklist for LEA-5

Designing-in a LEA-5 GPS/GALILEO receiver is easy especially when a design is based on the reference design in the Hardware Integration Manual. Nonetheless, it pays to do a quick sanity check of the design. This section lists the most important items for a simple design check. The Layout Design-In Checklist also helps to avoid an unnecessary respin of the PCB and helps to achieve the best possible performance.

It is highly recommended to follow the Design-In Checklist when developing any u-blox 5 GPS/GALILEO applications. This can significantly reduce development time and costs.

#### Have you chosen the optimal module?

|     | ,                                                                                                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | -5 modules have been intentionally designed to allow GPS/GALILEO receivers to be optimally tailored to cific applications. Changing between the different variants is easy.                                                    |

|     | Do you need Kick-start performance – Then choose a LEA-5 <b>H</b> , LEA-5 <b>S</b> , or LEA-5 <b>Q</b> .                                                                                                                       |

|     | Do you want to be able to upgrade the firmware or to permanently save configuration settings? Then you will have to use a Programmable receiver module: choose a LEA-5 <b>H</b> .                                              |

|     | Do you need USB – Then choose a LEA-5 $\mathbf{H}$ , LEA-5 $\mathbf{M}$ , or LEA-5 $\mathbf{Q}$ . Please note that LEA-5 $\mathbf{S}$ , and LEA-5 $\mathbf{A}$ do not yet support USB. See Section 2.3.2 for more information. |

|     | Do you need Precision Timing – Then choose a LEA-5 <b>T</b> .                                                                                                                                                                  |

| Che | ck Power Supply Requirements and Schematic:                                                                                                                                                                                    |

|     | Is the power supply within the specified range?                                                                                                                                                                                |

|     | Is the voltage <b>VDDUSB</b> within the specified range?                                                                                                                                                                       |

|     | Compare the peak current consumption of LEA-5 with the specification of your power supply.                                                                                                                                     |

|     | GPS receivers require a stable power supply, avoid ripple on VCC (<50mVpp)                                                                                                                                                     |

| Вас | kup Battery                                                                                                                                                                                                                    |

|     | For achieving a minimal Time To First Fix (TTFF) after a power down, make sure to connect a backup battery to <b>V_BCKP</b> .                                                                                                  |

| Ant | enna                                                                                                                                                                                                                           |

|     | The total noise figure should be well below 3dB.                                                                                                                                                                               |

|     | If a patch antenna is the preferred antenna, choose a patch of at least 15x15mm. Designs using smaller antennas require aiding.                                                                                                |

|     | Make sure the antenna is not placed close to noisy parts of the circuitry. (e.g. micro-controller, display, etc.)                                                                                                              |

|     | For active antennas add a 10R resistor in front of $V\_ANT^3$ input for short circuit protection or use the antenna supervisor circuitry.                                                                                      |

| Sch | ematic                                                                                                                                                                                                                         |

|     | If required, does your schematic allow using different LEA-5 variants?                                                                                                                                                         |

|     | Don't drive <b>RESET_N</b> high!                                                                                                                                                                                               |

|     | Plan use of 2 <sup>nd</sup> interface (Testpoints on serial port, DDC or USB) for firmware updates or as a service connector.                                                                                                  |

<sup>&</sup>lt;sup>3</sup> Only available with LEA-5-H, LEA-5S, LEA-5A, LEA-5T

# 2.6 LEA-5 Design

For a minimal Design with LEA-5 the following functions and pins need to be considered:

- Connect the Power supply to VCC.

- VDDUSB: Connect the USB power supply to a LDO before feeding it to VDDUSB and VCC. Or connect to GND if USB is not used.

- Assure a optimal ground connection to all ground pins of the LEA module

- Connect the antenna to **RF\_IN** over a matching 50 Ohm micro strip and define the antenna supply  $(\mathbf{V_ANT})^4$  for active antennas (internal or external power supply)

- Choose the required serial communication interface (USART, USB or DDC) and connect the appropriate pins to your application

- If you need Hot- or Warmstart in your application, connect a Backup Battery to V\_BCKP

- Decide whether **TIMEPULSE** or **RESET\_N** options are required in your application and connect the appropriate pins on your module

# 2.6.1 LEA-5 Passive Antenna Design (LEA-5-H, LEA-5S, LEA-5A, LEA-5T)

This is a minimal setup for a PVT GPS/GALILEO receiver.

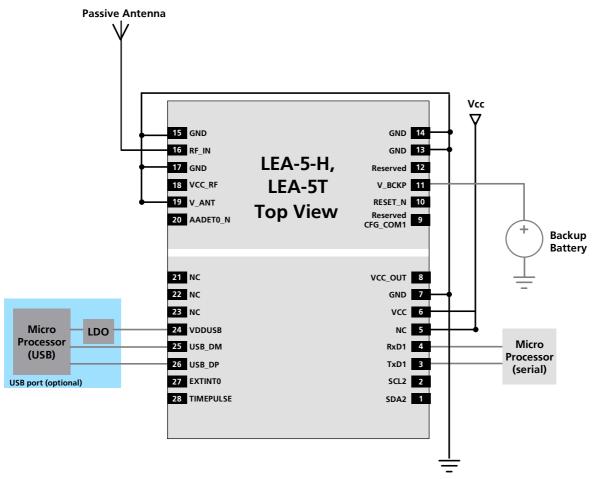

Figure 5: Passive Antenna Design for LEA-5-H, LEA-5T Receivers

-

$<sup>^{</sup> t 4}$  Only available with LEA-5-H, LEA-5S, LEA-5A, LEA-5T

Figure 6: Passive Antenna Design for LEA-5S, LEA-5A Receivers

| Function              | PIN              | I/O | Description                                 | Remarks                                                                                                                                                                                                                                                              |

|-----------------------|------------------|-----|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                 |                  |     |                                             |                                                                                                                                                                                                                                                                      |

| VCC                   | 6                | I   | Supply Voltage                              | Provide clean and stable supply.                                                                                                                                                                                                                                     |

| GND                   | 7, 13-<br>15, 17 | I   | Ground                                      | Assure a good <b>GND</b> connection to all <b>GND</b> pins of the module, preferably with a large ground.                                                                                                                                                            |

| VCC_OUT               | 8                | 0   |                                             | Connected to VCC. Leave open if not used.                                                                                                                                                                                                                            |

| V_BCKP                | 11               | I   | Backup voltage<br>supply                    | It's recommended to connect a backup battery to <b>V_BCKP</b> in order to enable Warm and Hot Start features on the receivers. Otherwise connect to <b>GND</b> (or <b>VCC</b> ).                                                                                     |

| VDDUSB                | 24               | I   | USB Power Supply                            | To use the USB interface connect this pin to 3.0 – 3.6V derived from VBUS. If no USB serial port used connect to GND.                                                                                                                                                |

| Antenna               |                  |     |                                             |                                                                                                                                                                                                                                                                      |

| RF_IN                 | 16               | I   | GPS/GALILEO<br>signal input from<br>antenna | Use a controlled impedance transmission line of 50 Ohm to connect to RF_IN. Don't supply DC through this pin. Use <b>V_ANT</b> pin to supply power.                                                                                                                  |

| VCC_RF                | 18               | 0   | Output Voltage RF section                   | Can be used to power an external active antenna (VCC_RF connected to V_ANT). The max power consumption of the Antenna must not exceed the datasheet specification of the module.  Leave open if not used.                                                            |

| V_ANT                 | 19               | I   | Antenna Bias<br>voltage                     | Connect to <b>GND</b> (or leave open) if Passive Antenna is used. If an active Antenna is used, add a 10R resistor in front of <b>V_ANT</b> input to the Antenna Bias Voltage or <b>VCC_RF</b> for short circuit protection or use the antenna supervisor circuitry. |

| AADETO_N              | 20               | I   | Active Antenna<br>Detect                    | Input pin for optional antenna supervisor circuitry. Leave open if not used.                                                                                                                                                                                         |

| Serial Port /USB      |                  |     |                                             |                                                                                                                                                                                                                                                                      |

| TxD1                  | 3                | 0   | Serial Port 1                               | Serial port output. Leave open if not used.                                                                                                                                                                                                                          |

| RxD1                  | 4                | I   | Serial Port 1                               | Serial port input with internal pull-up resistor to VCC. Leave open if not used.  Don't use an external pull up resistor.                                                                                                                                            |

| USB_DM <sup>5</sup>   | 25               |     |                                             | USB2.0 bidirectional communication pin. Leave open if unused. Implementation                                                                                                                                                                                         |

| USB DP <sup>5</sup>   | 26               | 1/0 | USB I/O line                                | see Section 2.3.2.                                                                                                                                                                                                                                                   |

| System                |                  |     |                                             |                                                                                                                                                                                                                                                                      |

| RESET_N               | 10               | I   | Hardware Reset<br>(Active Low)              | Leave open if not used. Do not drive high.                                                                                                                                                                                                                           |

| TIMEPULSE             | 28               | 0   | Timepulse Signal                            | Configurable Timepulse signal (one pulse per second by default). Leave open if not used.                                                                                                                                                                             |

| EXTINT0               | 27               | I   | External Interrupt                          | External Interrupt Pin. Internal pull-up resistor to <b>VCC</b> . Leave open if not used.                                                                                                                                                                            |

| CFG_COM1/<br>Reserved | 9                | I   | Configuration Pin/<br>Reserved              | LEA-5S, LEA-5A: Leave open for default configuration. LEA-5H, LEA-5T: Reserved                                                                                                                                                                                       |

| SDA2                  | 1                | 1/0 | DDC Dina                                    | DDC Data. Leave open if not used.                                                                                                                                                                                                                                    |

| SCL2                  | 2                | I/O | DDC Pins                                    | DDC Clock. Leave open if not used.                                                                                                                                                                                                                                   |

| Reserved              | 12               | I   |                                             | Leave open, do not drive low.                                                                                                                                                                                                                                        |

| NC                    | 5                |     |                                             | Can be left open, but <b>connection to VCC is recommended</b> for compatibility reasons. I/O voltage is always VCC.                                                                                                                                                  |

| NC                    | 21-22            |     | Not Connect                                 | Leave open                                                                                                                                                                                                                                                           |

| NC                    | 23               |     | Not Connect                                 | Leave open                                                                                                                                                                                                                                                           |

Table 4: Pinout LEA-5-H, LEA-5S, LEA-5A, LEA-5T

$<sup>^{\</sup>scriptscriptstyle 5}$  Planned availability Q1/09 for LEA-5S and LEA-5A

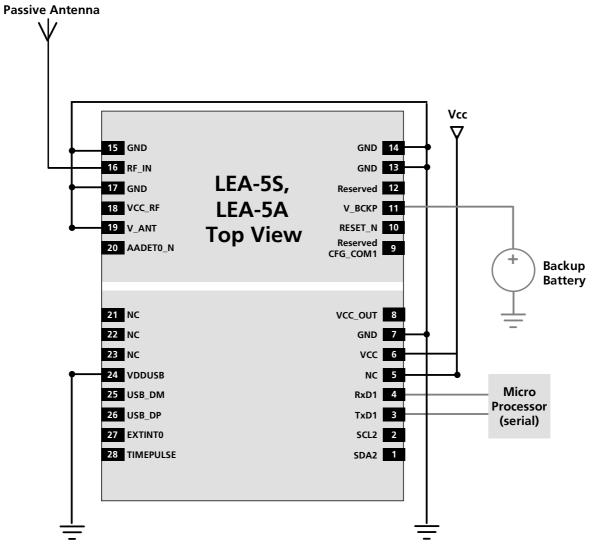

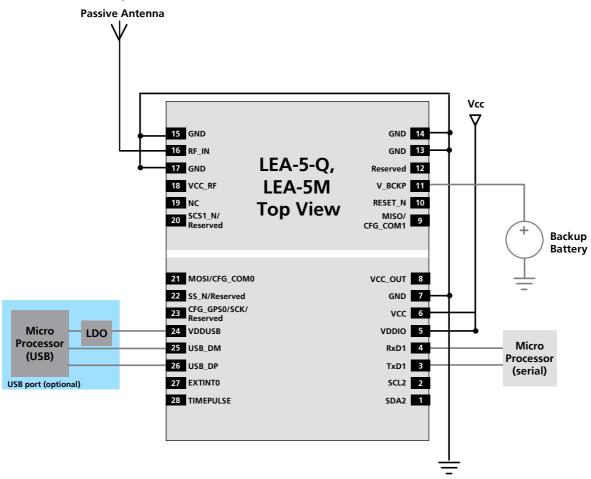

# 2.6.2 Passive Antenna Design (LEA-5-Q, LEA-5M)

This is a minimal setup for a PVT GPS/GALILEO receiver.

Figure 7: Pinout LEA-5-Q, LEA-5M

| Function                 | PIN              | I/O | Description                                 | Remarks                                                                                                                                                                                                                                                 |

|--------------------------|------------------|-----|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                    |                  |     |                                             |                                                                                                                                                                                                                                                         |

| VCC                      | 6                | I   | Supply Voltage                              | Provide clean and stable supply.                                                                                                                                                                                                                        |

| GND                      | 7, 13-<br>15, 17 | I   | Ground                                      | Assure a good <b>GND</b> connection to all <b>GND</b> pins of the module, preferably with a large ground plane.                                                                                                                                         |

| VCC_OUT                  | 8                | 0   |                                             | Connected to VCC. Leave open if not used.                                                                                                                                                                                                               |

| V_BCKP                   | 11               | I   | Backup voltage<br>supply                    | It's recommended to connect a backup battery to <b>V_BCKP</b> in order to enable Warm and Hot Start features on the receivers. Otherwise connect to <b>GND</b> (or VCC).                                                                                |

| VDDUSB                   | 24               | I   | USB Power Supply                            | To use the USB interface connect this pin to 3.0-3.6V derived from VBUS.  If no USB serial port used connect to GND.                                                                                                                                    |

| VDDIO                    | 5                | I   | I/O Voltage                                 | Defines the I/O voltage. Do not leave open.                                                                                                                                                                                                             |

| Antenna                  |                  |     |                                             |                                                                                                                                                                                                                                                         |

| RF_IN                    | 16               | I   | GPS/GALILEO<br>signal input from<br>antenna | Use a controlled impedance transmission line of 50 Ohm to connect to RF_IN. Antenna bias voltage for active antennas is not provided on the <b>RF_IN</b> pin. If an active Antenna is used an external voltage is required (see <i>Section 2.9.3</i> ). |

| VCC_RF                   | 18               | 0   | Output Voltage RF section                   | Leave open                                                                                                                                                                                                                                              |

| Serial Port /USB         |                  |     |                                             |                                                                                                                                                                                                                                                         |

| TxD1                     | 3                | 0   | Serial Port 1                               | Serial port output. Leave open if not used.                                                                                                                                                                                                             |

| RxD1                     | 4                | I   | Serial Port 1                               | Serial port input with internal pull-up resistor to VCC. Leave open if not used.                                                                                                                                                                        |

| LICD DA                  | 2.5              |     |                                             | Don't use an external pull up resistor.                                                                                                                                                                                                                 |

| USB_DM                   | 25<br>26         | 1/0 | USB I/O line                                | USB2.0 bidirectional communication pin. Leave open if unused. Implementation see Section 2.3.2.                                                                                                                                                         |

| USB_DP                   | 26               |     |                                             |                                                                                                                                                                                                                                                         |

| System                   |                  | 1   | Hardware Reset                              | Leave open if not used. Do not drive high.                                                                                                                                                                                                              |

| RESET_N                  | 10               | I   | (Active Low)                                | ·                                                                                                                                                                                                                                                       |

| TIMEPULSE                | 28               | 0   | Timepulse Signal                            | Configurable Timepulse signal (one pulse per second by default). Leave open if not used.                                                                                                                                                                |

| EXTINT0                  | 27               | I   | External Interrupt                          | External Interrupt Pin. Internal pull-up resistor to <b>VCC</b> . Leave open if not used.                                                                                                                                                               |

| SDA2                     | 1                |     |                                             | DDC Data. Leave open, if not used.                                                                                                                                                                                                                      |

| SCL2                     | 2                | 1/0 | DDC Pins                                    | DDC Clock. Leave open, if not used.                                                                                                                                                                                                                     |

| Reserved                 | 12               | I   |                                             | Leave open, do not drive low.                                                                                                                                                                                                                           |

| NC                       | 19               |     | Not Connected                               | Leave open.                                                                                                                                                                                                                                             |

| SCS1_N/<br>Reserved      | 20               | 0   | SPI                                         | LEA-5Q: SPI Chip Select. Leave open if not used.<br>LEA-5M: Leave open.                                                                                                                                                                                 |

| MISO/<br>CFG_COM1        | 9                | 1/0 | SPI<br>Configuration Pin                    | LEA-5Q: SPI MISO. Leave open, if not used.<br>LEA-5Q/LEA-5M: Leave open for default configuration.                                                                                                                                                      |

| MOSI/<br>CFG_COM0        | 21               | 1/0 | SPI<br>Configuration Pin                    | LEA-5Q: SPI MOSI. Leave open, if not used.<br>LEA-5Q/LEA-5M: Leave open for default configuration.                                                                                                                                                      |

| SS_N/<br>Reserved        | 22               | I   | SPI<br>Reserved                             | LEA-5Q: SPI Slave Select. Leave open, if not used.<br>LEA-5M: Leave open.                                                                                                                                                                               |

| SCK/CFG_GPS/<br>Reserved | 23               | 1/0 | SPI/Power Mode                              | LEA-5Q: SPI Clock / Power Mode Configuration Pin. Leave open, if not used.<br>LEA-5M: Leave open.                                                                                                                                                       |

Table 5: Pinout LEA-5-Q, LEA-5M

# 2.7 Layout Design-In Checklist

Follow this checklist for the Layout design to get an optimal GPS performance.

# Layout optimizations (Section 2.8)

- □ Is the GPS module placed according to the recommendation in Section 2.8.3?

- ☐ Has the Grounding concept been followed (see Section 2.8.4)?

- ☐ Has the micro strip been kept as short as possible?

- Add a ground plane underneath the GPS module to reduce interference.

- ☐ For improved shielding, add as many vias as possible around the micro strip, around the serial communication lines, underneath the GPS module etc.

#### Calculation of the micro strip (Section 2.8.5)

- ☐ The micro strip must be 50 Ohms and be routed in a section of the PCB where minimal interference from noise sources can be expected.

- In case of a multi-layer PCB, use the thickness of the dielectric between the signal and the 1st **GND** layer (typically the 2nd layer) for the micro strip calculation.

- If the distance between the micro strip and the adjacent **GND** area (on the same layer) does not exceed 5 times the track width of the micro strip, use the "Coplanar Waveguide" model in AppCad to calculate the micro strip and not the "micro strip" model.

# 2.8 Layout

This section provides important information for designing a reliable and sensitive GPS/GALILEO system.

GPS signals at the surface of the Earth are about 15dB below the thermal noise floor. Signal loss at the antenna and the RF connection must be minimized as much as possible. When defining a GPS receiver layout, the placement of the antenna with respect to the receiver, as well as grounding, shielding and jamming from other digital devices are crucial issues and need to be considered very carefully.

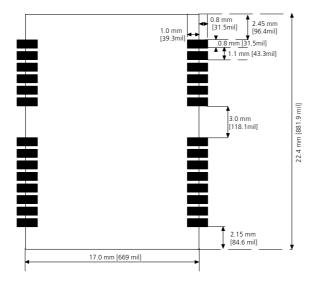

# 2.8.1 Footprint

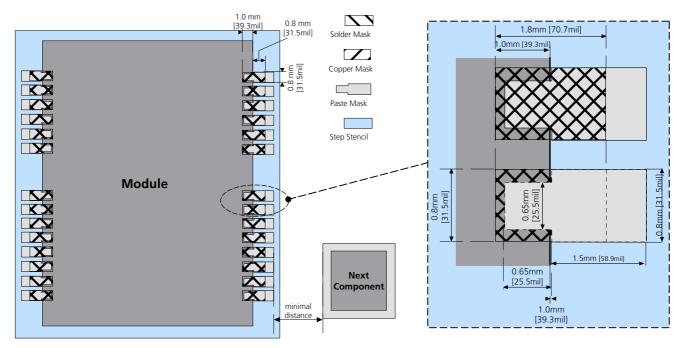

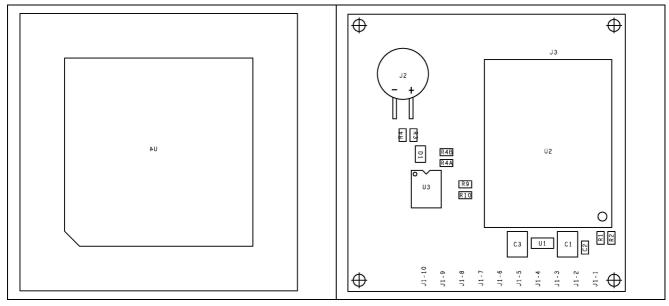

Figure 8: Recommended footprint

# 2.8.2 Paste Mask

Figure 9 shows the recommended positioning of the Paste Mask, the Copper and Solder masks, as well as the step stencil. These are recommendations only and not specifications. Note that the Copper and Solder masks have the same size and position.

To improve the wetting of the half vias, reduce the amount of solder paste under the module and increase the volume outside of the module by defining the dimensions of the paste mask to form a T-shape (or equivalent) extending beyond the Copper mask as shown in Figure 9. In addition, use a step stencil covering the entire area of the module and beyond the paste mask to increase the volume of solder paste here. The solder paste at the step stencil should have a total thickness of 175 to 200  $\mu$ m.

If a step stencil is not used it is still advisable to increase the volume of solder paste **outside** the module to attain the desired level of wetting. This must be done by modifying the shape of the paste mask outside the module, to allow for the increased volume of solder paste.

Figure 9: Recommendations for copper, solder and paste masks with enlargement

The paste mask outline needs to be considered when defining the minimal distance to the next component.

The exact geometry, distances, stencil thicknesses, step heights and solder paste volumes must be adapted to the specific production processes (e.g. soldering etc.) of the customer.

# 2.8.3 Placement

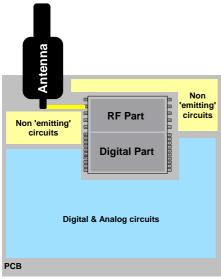

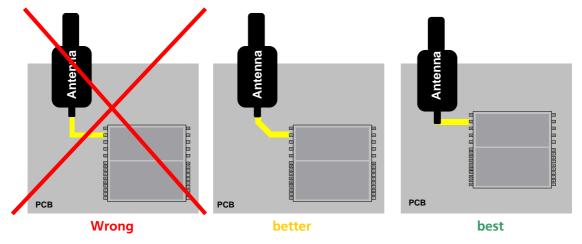

A very important factor in achieving maximum GPS and GALILEO performance is the placement of the receiver on the PCB. The connection to the antenna must be as short as possible to avoid jamming into the very sensitive RF section.

Make sure that RF critical circuits are clearly separated from any other digital circuits on the system board. To achieve this, position the receiver digital part towards your digital section of the system PCB. Care must also be exercised with placing the receiver in proximity to circuitry that can emit heat. The RF part of the receiver is very sensitive to temperature and sudden changes can have an adverse impact on performance.

The RF part of the receiver is a temperature sensitive component. Avoid high temperature drift and air vents near the receiver.

# 2.8.4 Antenna Connection and Grounding Plane Design

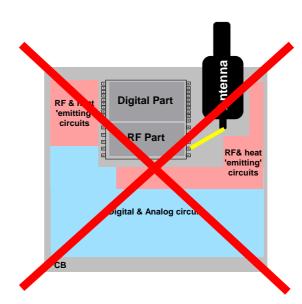

u-blox 5 modules can be connected to passive patch or active antennas. The RF connection is on the PCB and connects the **RF\_IN** pin with the antenna feed point or the signal pin of the connector, respectively. *Figure 11* illustrates connection to a typical five-pin RF connector. One can see the improved shielding for digital lines as discussed in *Appendix* D.3. Depending on the actual size of the ground area, additional vias should be placed in the outer region. In particular, the edges of the ground area should be terminated with a dense line of vias.

Figure 11: Recommended layout

As seen in *Figure 11*, an isolated ground area is created around and below the RF connection. This part of the circuit MUST be kept as far from potential noise sources as possible. Make certain that no signal lines cross, and that no signal trace vias appear at the PCB surface within the area of the red rectangle. The ground plane should also be free of digital supply return currents in this area. On a multi layer board, the whole layer stack below the RF connection should be kept free of digital lines. This is because even solid ground planes provide only limited isolation.

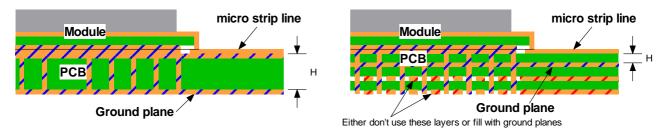

The impedance of the antenna connection has to match the 50 Ohm impedance of the receiver. To achieve an impedance of 50 Ohms, the width W of the micro strip has to be chosen depending on the dielectric thickness H, the dielectric constant  $\varepsilon_r$  of the dielectric material of the PCB and on the build-up of the PCB (see *Section 2.8.5*). *Figure 12* shows two different builds: A 2 Layer PCB and a 4 Layer PCB. The reference ground plane is in both designs on layer 2 (red). Therefore the effective thickness of the dielectric is different.

Figure 12: PCB build-up for Micro strip line. Left: 2-layer PCB, right: 4-layer PCB

General design recommendations:

- The length of the micro strip line should be kept as short as possible. Lengths over 2.5 cm (1 inch) should be avoided on standard PCB material and without additional shielding.

- Distance between micro strip line and ground area on the top layer should at least be as large as the dielectric thickness.

- Routing the RF connection close to digital sections of the design should be avoided.

- To reduce signal reflections, sharp angles in the routing of the micro strip line should be avoided. Chamfers or fillets are preferred for rectangular routing; 45-degree routing is preferred over Manhattan style 90-degree routing.

- Routing of the RF-connection underneath the receiver should be avoided. The distance of the micro strip line to the ground plane on the bottom side of the receiver is very small (some 100 µm) and has huge tolerances (up to 100%). Therefore, the impedance of this part of the trace cannot be controlled.

- Use as many vias as possible to connect the ground planes.

- In order to avoid reliability hazards, the area on the PCB under the receiver should be entirely covered with solder mask. Vias should not be open.

# 2.8.5 Antenna Micro Strip

There are many ways to design wave-guides on printed circuit boards. Common to all is that calculation of the electrical parameters is not straightforward. Freeware tools like AppCAD from Agilent or TXLine from Applied Wave Research, Inc. are of great help. They can be downloaded from <a href="https://www.agilent.com">www.agilent.com</a> and <a href="https://www

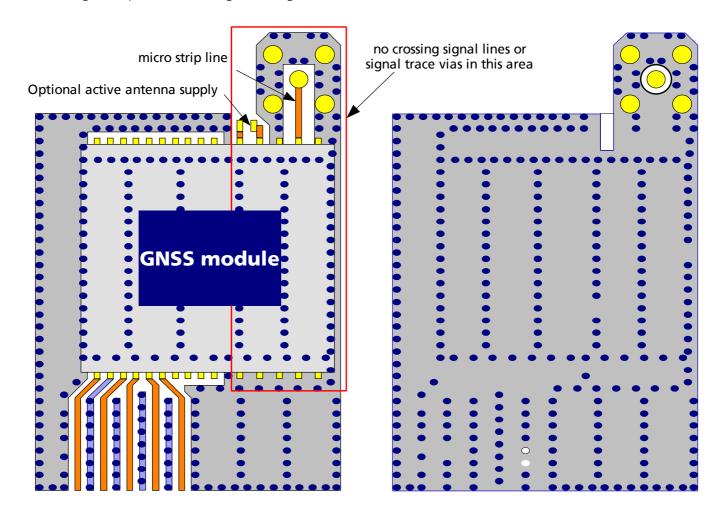

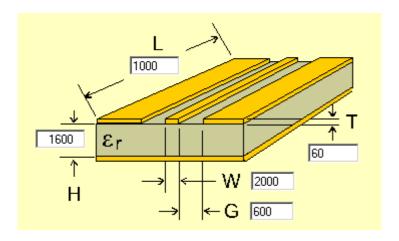

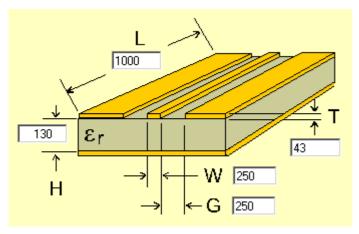

The micro strip is the most common configuration for printed circuit boards. The basic configuration is shown in *Figure 13* and *Figure 14*. As a rule of thumb, for a FR-4 material the width of the conductor is roughly double the thickness of the dielectric to achieve 50 Ohms line impedance.

For the correct calculation of the micro strip impedance, one does not only need to consider the distance between the top and the first inner layer but also the distance between the micro strip and the adjacent GND plane on the same layer

Use the Coplanar Waveguide model for the calculation of the micro strip.

Figure 13: Micro strip on a 2-layer board (Agilent AppCAD Coplanar Waveguide)

Figure 13 shows an example of a 2-layer FR4 board of 1.6 mm thickness and a 35 $\mu$ m (1 once) copper cladding. The thickness of the micro strip is comprised of the cladding (35 $\mu$ m) plus the plated cupper (typically 25 $\mu$ m). Figure 14 depicts an example of a multi layer FR4 board with 18 $\mu$ m (½ once) cladding and 180 $\mu$  dielectric between layer 1 and 2.

Figure 14: Micro strip on a multi layer board (Agilent AppCAD Coplanar Waveguide)

# 2.9 Antenna and Antenna Supervisor

u-blox 5 modules receive L1 band signals from GPS and GALILEO satellites at a nominal frequency of 1575.42 MHz. The RF signal is connected to the **RF IN** pin.

u-blox 5 modules can be connected to passive or active antennas.

For u-blox 5 receivers, the total preamplifier gain (minus cable and interconnect losses) must not exceed 50 dB. Total noise figure should be below 3 dB.

The u-blox 5 Technology supports either a short circuit protection of the active antenna or an active antenna supervisor circuit (open and short circuit detection). For further information refer to Section 2.9.2).

# 2.9.1 Passive Antenna

A design using a passive antenna requires more attention regarding the layout of the RF section. Typically a passive antenna is located near electronic components; therefore care should be taken to reduce electrical 'noise' that may interfere with the antenna performance. Passive antennas do not require a DC bias voltage and can be directly connected to the RF input pin **RF\_IN**. Sometimes, they may also need a passive matching network to match the impedance to 50 Ohms.

Some passive antenna designs present a DC short to the RF input, when connected. If a system is designed with antenna bias supply AND there is a chance of a passive antenna being connected to the design, consider a short circuit protection.

All u-blox 5 receivers have a built-in LNA required for passive antennas.

# 2.9.2 Active Antenna (LEA-5-H, LEA-5S, LEA-5A, LEA-5T)

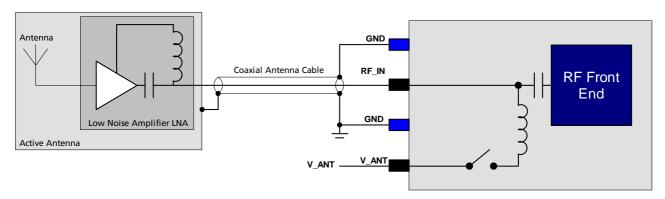

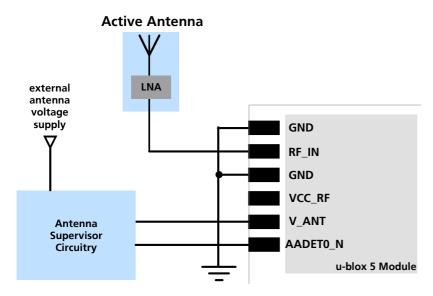

Active antennas have an integrated low-noise amplifier. They can be directly connected to **RF\_IN**. If an active antenna is connected to **RF\_IN**, the integrated low-noise amplifier of the antenna needs to be supplied with the correct voltage through pin **V\_ANT** or an external inductor. Usually, the supply voltage is fed to the antenna through the coaxial RF cable. Active antennas require a power supply that will contribute to the total GPS system power consumption budget with additional 5 to 20 mA typically. Inside the antenna, the DC component on the inner conductor will be separated from the RF signal and routed to the supply pin of the LNA (see Figure 15).

Figure 15: Active antenna biasing

Generally an active antenna is easier to integrate into a system design, as it is less sensitive to jamming compared to a passive antenna. But an active antenna must also be placed far from any noise sources to have good performance.

Antennas should only be connected to the receiver when the receiver is not powered. Do not connect or disconnect the Antenna when the u-blox 5 receiver is running as the receiver calibrates the noise floor on power-up. Connecting the antenna after power-up can result in prolonged acquisition time.

Never feed supply voltage into RF\_IN. Always feed via V\_ANT or an external inductor .

To test GPS/GALILEO signal reacquisition, it is recommended to physically block the signal to the antenna, rather than disconnecting and reconnecting the receiver.

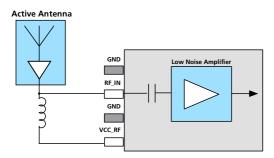

# 2.9.3 Active Antenna (LEA-5-Q, LEA-5M)

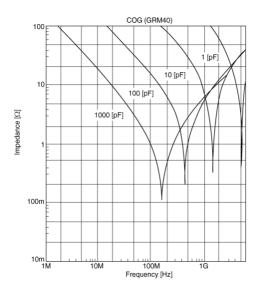

LEA-5-Q and LEA-5M modules do not provide the antenna bias voltage for active antennas on the **RF\_IN** pin. It is therefore necessary to provide this voltage outside the module via an inductor as indicated in Figure 16. u-blox recommends using an inductor from Coilcraft (0402CS-36NX). Alternative parts can be used if the inductor's resonant frequency matches the GPS frequency of 1575.4MHz.

Figure 16: Recommended wiring for active antennas

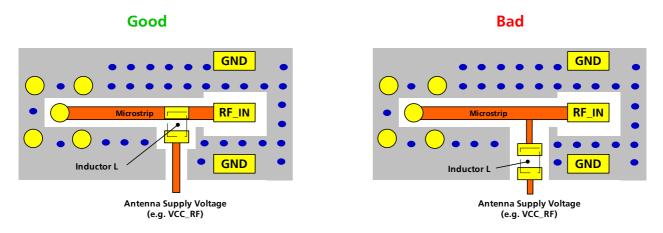

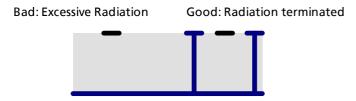

For optimal performance, it is important to place the inductor as close to the microstrip as possible. Figure 15 illustrates the recommended layout and how it should not be done.

Figure 17: Recommended layout for connecting the antenna bias voltage for LEA-5-Q and LEA-5M

# 2.9.4 Active Antenna Bias Power (LEA-5-H, LEA-5S, LEA-5A, LEA-5T)

There are two ways to supply the bias voltage to pin **V\_ANT**. It can be supplied externally (please consider the datasheet specification) or internally. For Internal supply, the **VCC\_RF** output must be connected to **V\_ANT** to supply the antenna with a filtered supply voltage. However, the voltage specification of the antenna has to match the actual supply voltage of the u-blox 5 Receiver (e.g. 3.0 V).

Figure 18: Supplying Antenna bias voltage

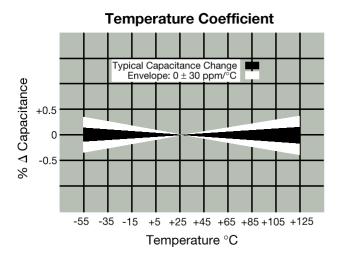

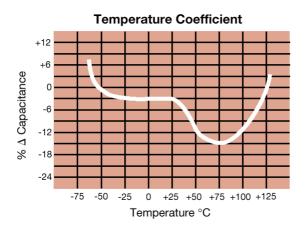

Since the bias voltage is fed into the most sensitive part of the receiver, i.e. the RF input, this supply should be virtually free of noise. Usually, low frequency noise is less critical than digital noise with spurious frequencies with harmonics up to the GPS/GALILEO band of 1.575 GHz. Therefore, it is not recommended to use digital supply nets to feed pin **V ANT**.

An internal switch (under control of the u-blox 5 software) can shutdown the supply to the external antenna whenever it is not needed. This feature helps to reduce power consumption.

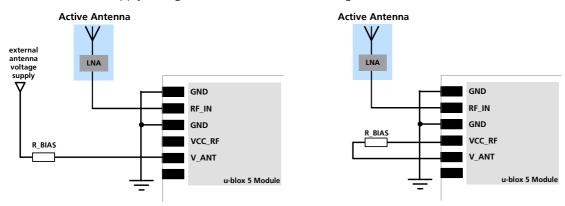

# 2.9.4.1 Short Circuit Protection

If a reasonably dimensioned series resistor **R\_BIAS** is placed in front of pin **V\_ANT**, a short circuit situation can be detected by the baseband processor. If such a situation is detected, the baseband processor will shut down supply to the antenna. The receiver is by default configured to attempt to reestablish antenna power supply periodically.

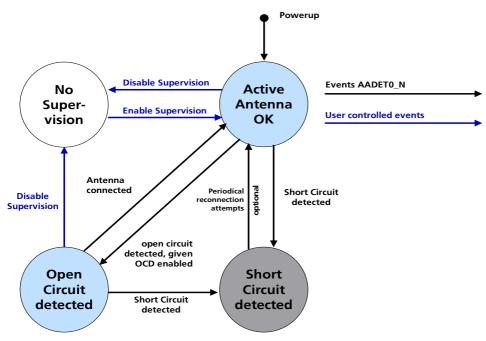

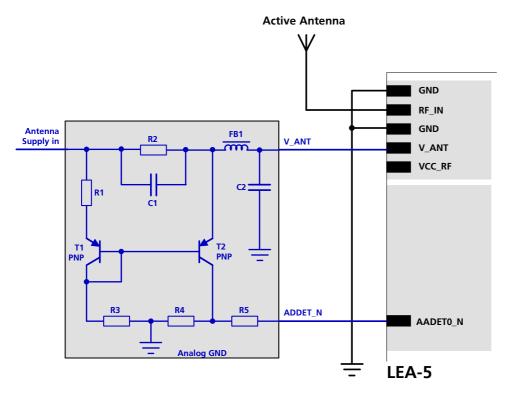

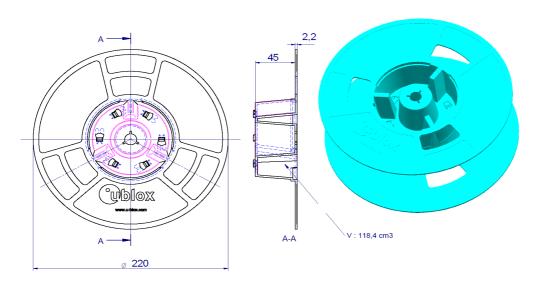

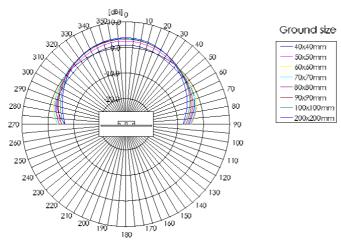

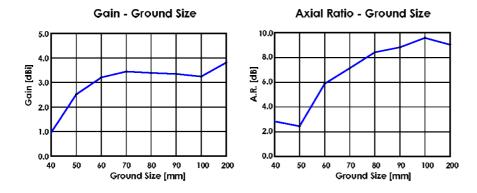

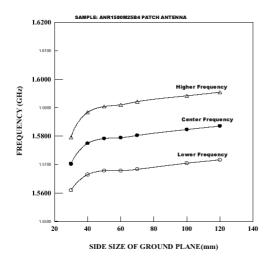

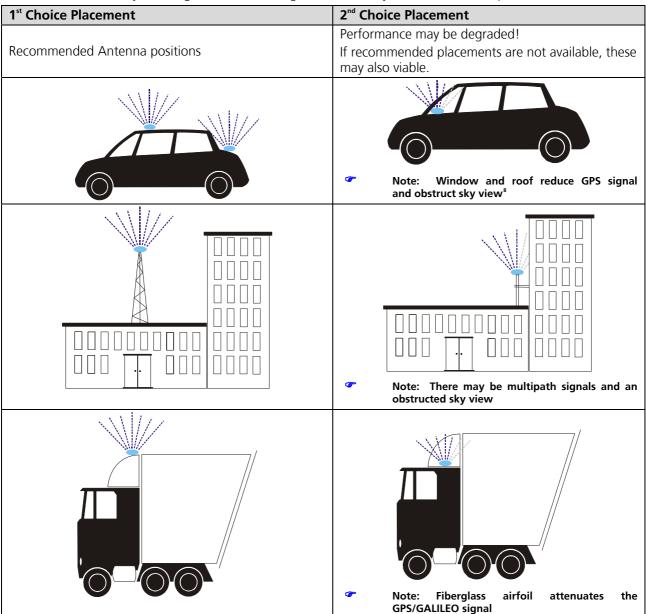

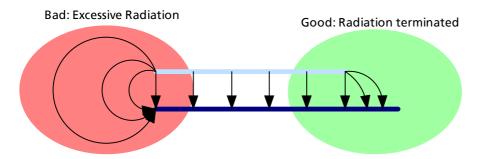

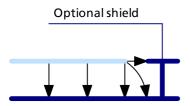

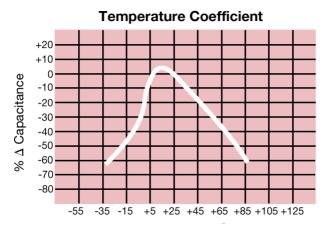

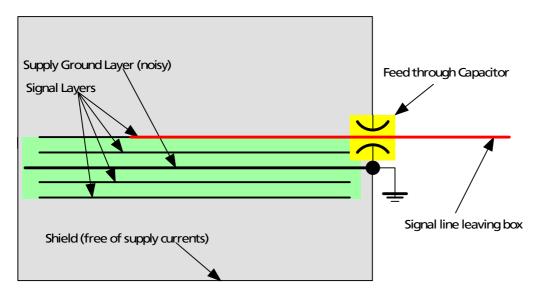

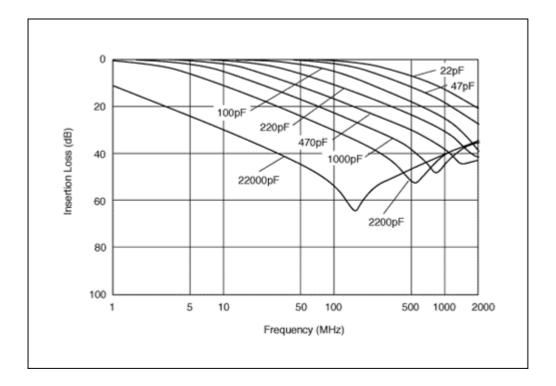

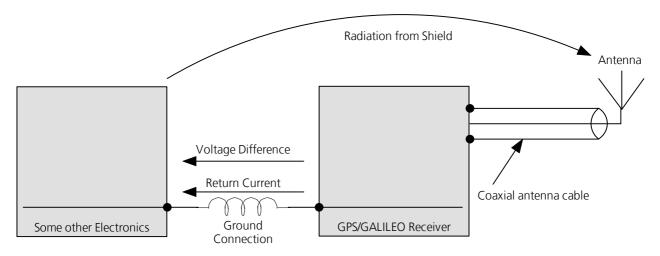

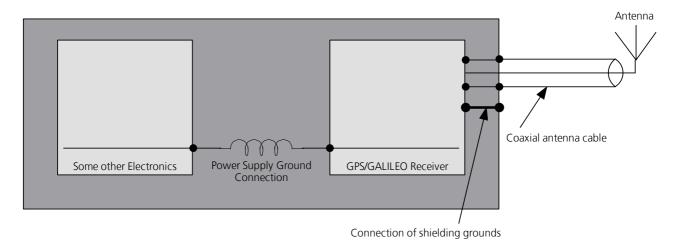

To configure the antenna supervisor use the UBX-CFG-ANT message. For further information refer to the *u-blox 5 Protocol Specification* [1].